VGA Card using FPGA and VHDL

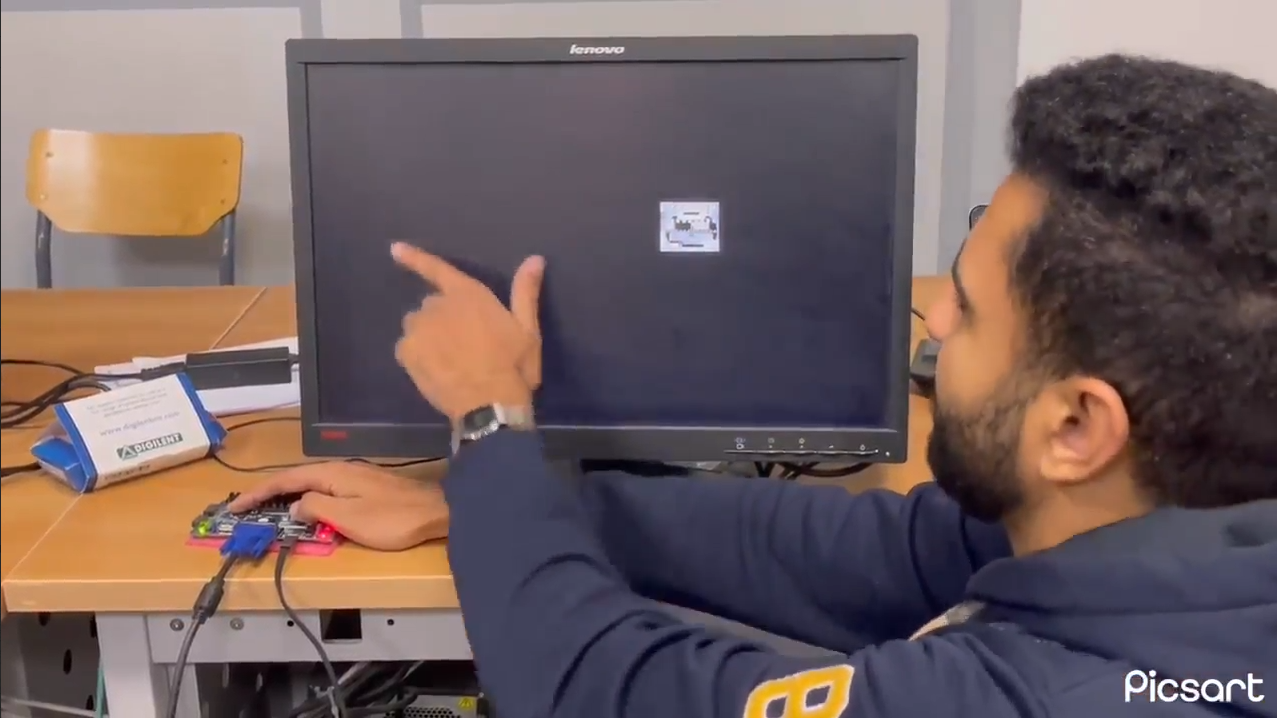

This project implements a basic VGA graphics controller on an FPGA using VHDL.

The design generates the required horizontal and vertical sync signals, timing counters, and pixel clock to drive a standard VGA monitor. A simple framebuffer or pattern generator provides pixel data, enabling test patterns and basic graphics output.

Key concepts:

- VGA timing generation (resolution, refresh rate, sync pulses)

- Finite state machines and counters in VHDL

- Mapping FPGA I/O pins to VGA connector signals

More detailed documentation, schematics, and code snippets are available in the document linked from the main Projects page.